Digital SOC IC Design

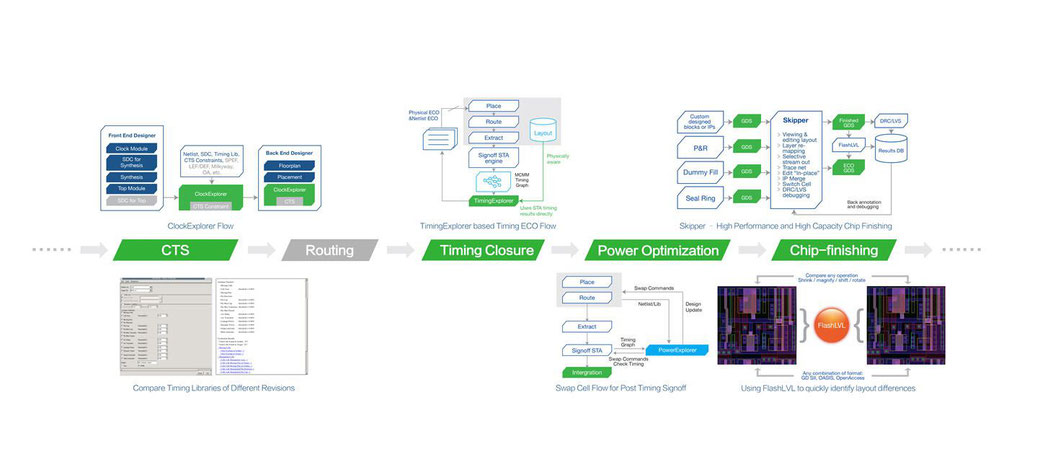

Empyrean provides SOC designers with solution to clock tree simplification and optimization, timing signoff automation and lib files analysis. Challenges in clock tree optimization and timing signoff come along with multi-scenario design methodology in progressive process, increasing difficulty of clock implementation and uncertainty to turn-around-time .

With powerful built-in engine, Empyrean could help engineers in clock tree optimization analyze clock structure, find potential problems, improve clock tree quality, and then enhance frequency, reduce power cost in clock network. To meet tight TAT in timing signoff stage, Empyrean supplies an integrated solution to hold/setup/trans fix with golden timing accuracy and smart automatic placement, which efficiently speed up timing signoff process and help designers deliver products on schedule.

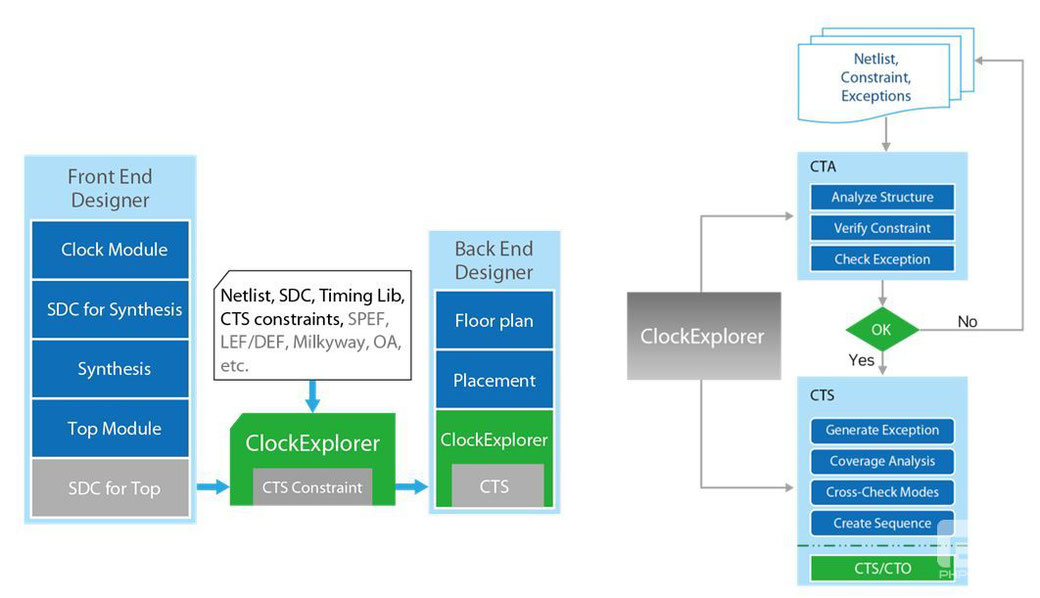

ClockExplorer

ClockExplorer analyzes clock structures and optimizes clock constraints to reduce insertion delay. The generated constraints are CTS-aware, enabling better clock tree generation. ClockExplorer also provides a comprehensive set of checking capabilities which are used by both the front-end and back-end design teams as a tool for sign-off/sign-in of clock constraints.

XTop

Current SoC design is growing +100M insts and +100 scenarios to sign-off, timing closure becomes much difficult and time consuming.

ICExplorer-XTop can provide best-in-class timing ECO solution with higher efficiency, lower cost and silicon accuracy.

Adv. Massively Parallel Architecture improves the performance and capacity very much Upg. Physical and Timing Opt. Engines can better support advanced process, better estimate the physical sensitivity and resolve the complicated violations New Timing-Inspection and Interactive-ECO Functions greatly improves the capability and efficiency of the last hot-paths Integrated with ICExplorer-XTime for much lower cost with silicon accurate timing.

XTime

STA sign-off no longer works below 16nm, esp. at low voltage, bad yield due to inaccurate timing and too much power and area cost by extra margin. ICExplorer-XTime is the answer for advanced process and ultra low power design (IoT)

SPICE Monte Carlo accuracy for timing calibration and extra margin recovery

Super parallel architecture and advanced fast Monte-Carlo algorithm make SPICE accurate timing sign-off possible, tens of the thousands of paths can be simulated within 1 day

Advanced BIG Data Analysis capability opens up a range of timing sign-off solutions, such as V/T sweeping, timing bottleneck analysis, sensitivity analysis …

Seamless integrated in ICExplorer-XTop platform for silicon accurate timing ECO with higher efficiency and lower cost

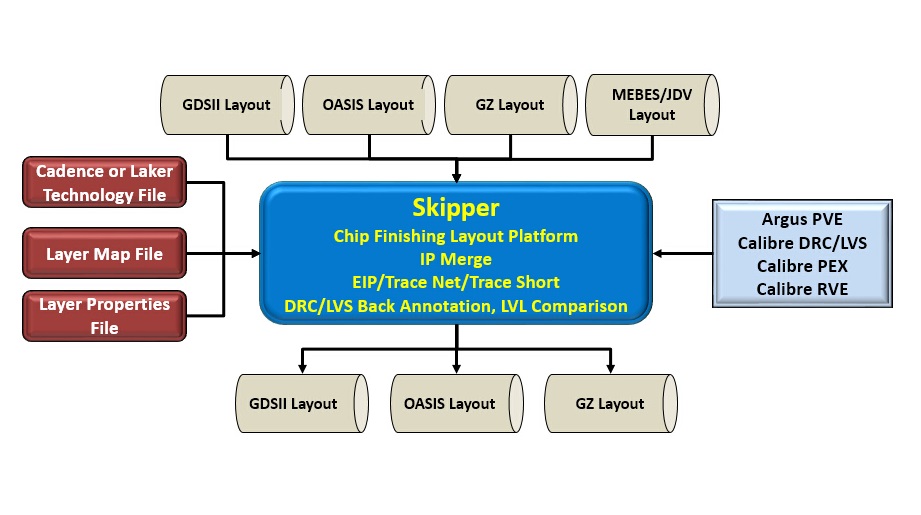

Skipper

Skipper is a high performance chip finishing tool with ultra large capacity.

It combines an optimized database and highly effective memory management. It can handle huge designs with 100GB GDS data and performs fast data import, management, editing and searching operations with relatively small system resources, greatly reducing update time.

FlashLVL

FlashLVL is a hierarchical and parallel layout comparison tool that meets the requirements of finding differences between two versions of layouts. By integrating with popular full-custom and mixed-signal IC design platforms, FlashLVL efficiently locates the changes, reduces verification time and improves productivity. FlashLVL has outstanding performance and many features, and provides designers with an effective layout comparison and verification solution.

Qualib

Qualib is a comprehensive timing library analysis tool that enables comparison of different revisions of a timing library or libraries based on different process corners or even different vendors.

Key Benefit:

Reduced risk

Key Features:

Comparison of timing libraries

Consistency checking between NLDM and CCS formats

Comprehensive analysis of timing and power characteristics

Built-in calculator for cell and interconnect timing

Contact Us:

Ambition Technologies

17-FF, Pocket 2, Sector 24

Rohini, New Delhi - 110085 India

Phone:

# 9810400671 / Pranay@ambitec.org

# 9911223020 / Rahul@ambitec.org

Email: sales@ambitec.org